Embedded wafer level ball grid array

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

|

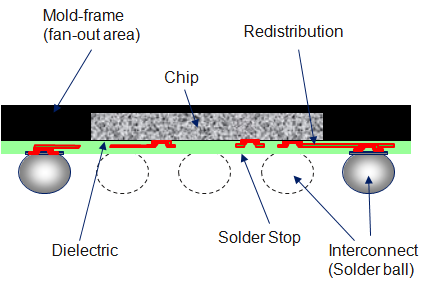

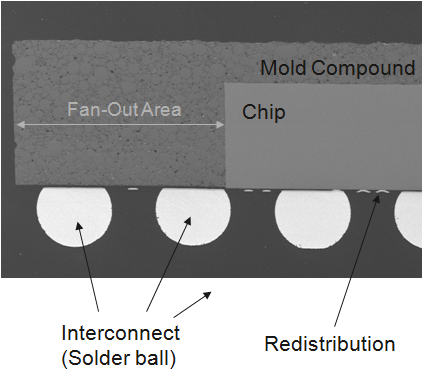

Embedded wafer level ball grid array (eWLB) is a packaging technology for integrated circuits. The package interconnects are applied on an artificial wafer made of silicon chips and a casting compound.

eWLB is a further development of the classical wafer level ball grid array technology (WLB or WLP: wafer level package). The main driving force behind the eWLB technology was to allow fanout and more space for interconnect routing.

All process steps for the generation of the package are performed on the wafer. This allows, in comparison to classical packaging technologies (e. g. ball grid array), the generation of very small and flat packages with excellent electrical and thermal performance at lowest cost. It is common for all WLB technologies, which are built on a silicon wafer, that the interconnects (typically solder balls) fit on the chip (so called fan-in design). Therefore only chips with a restricted number of interconnects can be packaged.

The eWLB technology allows the realization of chips with a high number of interconnects. The package is not created on a silicon wafer as for the classical wafer level package, but on an artificial wafer. Therefore a front-end-processed wafer is diced and the singulated chips are placed on a carrier. The distance between the chips can be chosen freely, but it is typically larger than on the silicon wafer. The gaps and the edges around the chips are now filled with a casting compound to form a wafer. After curing an artificial wafer containing a mold frame around the dies for carrying additional interconnect elements is created. After the build of the artificial wafer (the so-called reconstitution) the electrical connections from the chip pads to the interconnects are made in thin-film technology, as for any other classical wafer level package.

With this technology any number of additional interconnects can be realized on the package in an arbitrary distance (fan-out design). Therefore, this wafer level packaging technology can also be used for space sensitive applications, where the chip area wouldn’t be sufficient to place the required number of interconnects at a suitable distance. The eWLB technology was developed by Infineon, STMicroelectronics and STATS ChipPAC Ltd.[1] First components were brought into market mid of 2009 (mobile phone).

Process Steps[edit]

- Lamination of foil onto carrier (lamination tool)

- Chip placement onto wafer (pick and place tool)

- Molding (mold press)

- De-bonding of carrier (de-bonding tool)

- Flip reconstructed wafer

- Ball drop reflow and wafer test

Advantages[edit]

- Low cost (package and test)

- Minimal lateral package size and height

- Excellent electrical and thermal properties

- Number of realizable interconnects on the package is not restricted

- High integration potential for multi-die- and stacked packages

- Upcoming package standard

Disadvantages[edit]

- Inspection and repair difficult since visual inspection is restricted

- Mechanical stress between package and board is transmitted stronger than for other package technologies

See also[edit]

References[edit]

External links[edit]

- https://web.archive.org/web/20120305094749/http://www.infineonventures.com/cms/en/corporate/press/news/releases/2007/INFCOM200711-013.html

- http://content.yudu.com/Library/A1mxrk/3DPackagingFebruaryi/resources/4.htm

- https://safe.nrao.edu/wiki/pub/Main/EuropeanMicrowaveWeek08/WFR14-1.pdf

- https://web.archive.org/web/20080517033548/http://www.ciol.com/Semicon/Tech-Watch/News-Reports/Infineon,-ASE-intro-eWLB-package-technology/131107101404/0/

- http://www.statschippac.com/services/packagingservices/waferlevelproducts/~/media/Files/Package%20Datasheets/eWLB.ashx

- http://www.amkor.com/go/packaging/all-packages/cspnl/

- http://www.wsdmag.com/Articles/ArticleID/19576/19576.html

- http://www.semineedle.com/posting/26088?snc=20641&snc=20641[permanent dead link]

- http://ieeexplore.ieee.org/Xplore/login.jsp?url=http%3A%2F%2Fieeexplore.ieee.org%2Fiel5%2F4147209%2F4141004%2F04147210.pdf%3Farnumber%3D4147210&authDecision=-203

- https://web.archive.org/web/20110703111509/http://141.30.122.65/Keynotes/6-Plieninger-ESTC_Keynote_20060907.pdf

- https://web.archive.org/web/20090728202431/http://annualreport2008.infineon.com/de/template.asp?content=innovationen

- Seung Wook Yoon et al. Thermal and Electrical Characterization of eWLB (embedded Wafer Level BGA), Electronic Components and Technology Conference (ECTC), 2010